Históricamente, los procesadores han aumentado rápidamente el rendimiento de acuerdo con la «Ley de Moore» informal. La Ley de Moore es una observación de que la cantidad de transistores en los procesadores y, por lo tanto, la potencia de procesamiento de los procesadores, se duplica aproximadamente cada dos años.

La Ley de Moore se ha mantenido de manera bastante consistente durante décadas desde que se promulgó por primera vez en 1965, principalmente debido a los continuos avances de los fabricantes de procesadores en el tamaño de los transistores. Reducir el tamaño del transistor del procesador aumenta el rendimiento porque más transistores pueden caber en un espacio más pequeño y porque los componentes más pequeños son más eficientes energéticamente.

La ley de Moore está muerta

Sin embargo, de manera realista, la Ley de Moore nunca duraría para siempre, ya que cada vez es más difícil encoger los componentes a medida que se hacen pequeños. Desde 2010, en la escala de 14 y 10 nanómetros, o 10 mil millonésimas de metro, los fabricantes de procesadores han comenzado a toparse con el límite de lo que es físicamente posible. Los fabricantes de procesadores han luchado mucho para seguir reduciendo el tamaño del proceso por debajo de 10 nm, aunque a partir de 2020 hay chips de 7 nm disponibles y chips de 5 nm en la etapa de desarrollo.

Para combatir la falta de contracción del proceso, los fabricantes de procesadores tuvieron que usar otros métodos para seguir aumentando el rendimiento del procesador. Uno de esos métodos es simplemente hacer procesadores más grandes.

Producir

Uno de los problemas de crear un procesador increíblemente complejo como este es que la eficiencia del proceso no es del 100%. Algunos de los procesadores fabricados son simplemente defectuosos cuando se fabrican y deben desecharse. Al hacer un procesador más grande, el área de superficie más grande significa que hay una mayor probabilidad de que cada chip tenga un defecto que requiera descartarlo.

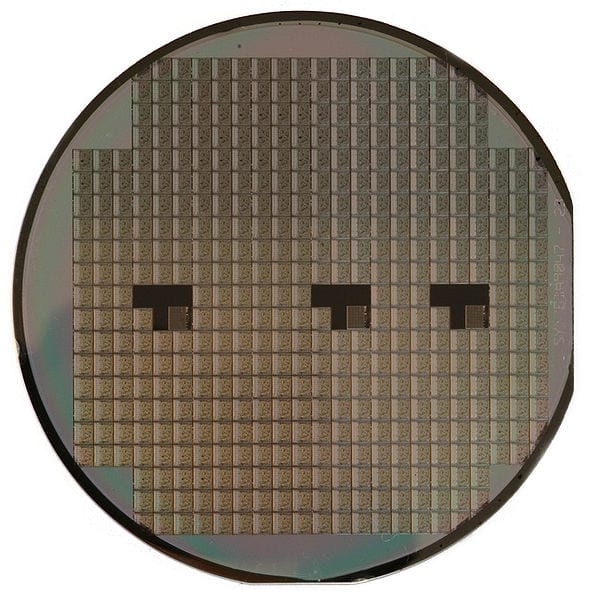

Los procesadores se fabrican en lotes, con muchos procesadores en una sola oblea de silicio. Por ejemplo, si estos segmentos contienen 20 errores cada uno en promedio, entonces se deberán descartar unos 20 procesadores por segmento. Con un diseño de CPU pequeño, podría haber, digamos, cien procesadores en un solo segmento; perder 20 no es genial, pero un retorno del 80% debería dar sus frutos. Sin embargo, con un diseño más grande, no se pueden colocar tantos procesadores en un solo segmento, con quizás solo 50 procesadores más grandes en un segmento. Perder 20 de esos 50 es mucho más doloroso y es mucho menos probable que valga la pena.

Nota: Los valores de este ejemplo se utilizan solo con fines de demostración y no son necesariamente representativos de los rendimientos reales.

Chiplets

Para combatir este problema, los fabricantes de procesadores han separado ciertas características y componentes en uno o más chips separados, aunque permanecen en el mismo paquete general. Estos chips separados son más pequeños que un solo chip monolítico y se conocen como «Chiplets».

Cada chiplet individual ni siquiera necesita utilizar el mismo nodo de proceso. Es muy posible tener chips basados en 7 nm y 14 nm en el mismo paquete general. El uso de un nodo de un proceso diferente puede ayudar a reducir los costos, ya que es más fácil crear nodos más grandes y los rendimientos son generalmente más altos porque la tecnología es menos avanzada.

Consejo: El nodo de proceso es el término que se utiliza para referirse a la escala de los transistores utilizados.

Por ejemplo, en los procesadores de servidor EPYC de segunda generación de AMD, los núcleos del procesador del procesador se distribuyen en ocho conjuntos de chips separados, cada uno de los cuales utiliza el nodo del procesador de 7 nm. También se utiliza un chiplet de nodo de 14 nm separado para manejar la E / S o la entrada / salida de los chiplets y todo el procesador.

Intel está diseñando algunos de sus futuros procesadores con dos chips de procesador separados, cada uno ejecutándose en un nodo de proceso diferente. La idea es que el antiguo nodo de despensa se puede usar para tareas que requieren menos energía, mientras que los núcleos de procesador de nodo más nuevos y más pequeños se pueden usar cuando se requiere el máximo rendimiento. El diseño que utiliza un nodo de cómputo dividido será particularmente útil para Intel, que ha tenido problemas para lograr eficiencias aceptables para su proceso de 10 nm.